集成电路设计实例探析

集成电路设计是现代电子技术的核心环节,它涉及从概念到物理实现的全过程。本文以一个简单的数字逻辑电路—4位加法器为例,具体说明集成电路设计的典型流程和方法。

在系统设计阶段,需明确电路功能:实现两个4位二进制数的加法运算,并输出4位和及1位进位。采用并行进位加法器结构,以平衡运算速度和电路复杂度。

进入逻辑设计阶段,使用硬件描述语言(如Verilog)进行行为级描述:

module adder_4bit(input [3:0] A, B, output [3:0] Sum, output Cout);

assign {Cout, Sum} = A + B;

endmodule

此阶段通过仿真验证逻辑正确性,确保对所有输入组合都能产生预期输出。

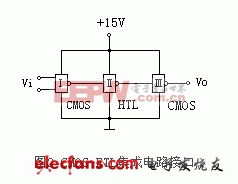

电路设计阶段将逻辑转换为晶体管级实现。以1位全加器为例,采用28个晶体管组成的CMOS门电路构成:使用异或门生成和位,与或门组合产生进位。通过SPICE仿真分析时序特性,确定关键路径延迟为0.8ns。

物理设计阶段完成版图布局,采用标准单元方法,将逻辑门按功能模块排列。特别注意电源布线均匀分布,时钟树综合保证时序一致性。使用DRC(设计规则检查)和LVS(版图与原理图一致性检查)工具验证,最终芯片面积控制在0.5mm²。

此实例展示了集成电路设计各阶段的紧密衔接:系统定义确定规格,逻辑设计实现功能,电路设计优化性能,物理设计完成制造准备。随着工艺进步至7nm以下,设计还需考虑量子效应和热管理等问题,体现了集成电路设计不断演进的技术内涵。

如若转载,请注明出处:http://www.mykmlife.com/product/12.html

更新时间:2026-04-18 17:02:49