CMOS集成电路设计(二) 接口电路详解

在CMOS集成电路设计中,接口电路是连接芯片内部逻辑与外部世界的关键桥梁。它不仅负责电平转换和信号驱动,还承担着保护内部电路、确保信号完整性和实现不同系统间兼容的重要职责。本文将深入探讨CMOS集成电路设计中几种核心接口电路的工作原理、设计要点及应用场景。

一、输入接口电路

输入接口电路的主要功能是将外部信号(可能具有不同的电压摆幅、噪声容限和驱动能力)安全、可靠地转换为芯片内部CMOS逻辑能够识别的信号。

- 施密特触发器输入:这是最常用的输入缓冲电路之一。其核心特点是具有迟滞特性,即上升阈值电压(VT+)高于下降阈值电压(VT-)。这一特性使其对缓慢变化的信号或带有严重噪声的信号具有极强的抗干扰能力,能有效防止信号在阈值附近抖动造成的误触发,从而产生干净、陡峭的输出波形。设计时需根据系统噪声容限和信号速率合理设定迟滞窗口。

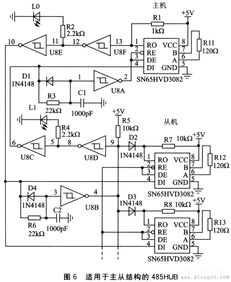

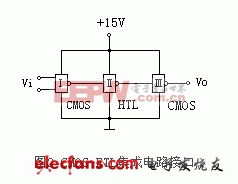

- 电平转换输入:当芯片需要与不同供电电压的逻辑系统(如1.8V、3.3V、5V系统)通信时,必须使用电平转换电路。简单的电阻分压网络可用于高压到低压的转换,但会引入信号完整性和驱动能力问题。更可靠的方法是采用专用的电平转换器电路,通常利用交叉耦合的PMOS/NMOS对,实现双向或单向的、低延迟的电平适配。

- ESD保护电路:所有输入/输出引脚都必须集成静电放电保护电路。典型的ESD保护结构包括基于二极管、栅接地NMOS或可控硅整流器的初级和次级保护网络,旨在将人体模型或机器模型产生的瞬间高压大电流安全泄放到电源或地线,防止脆弱的栅氧化层被击穿。

二、输出接口电路

输出接口电路的核心任务是将内部微弱的逻辑信号放大,以足够的电流和电压驱动外部负载(如PCB走线、其他芯片的输入、LED等)。

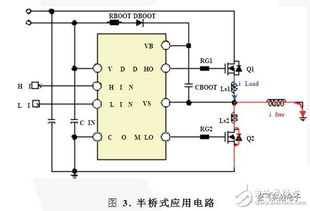

- 推挽输出级:这是最经典和常见的输出结构,由一个上拉PMOS管和一个下拉NMOS管组成互补对。其优点是结构简单、驱动能力强、输出电阻低、高低电平摆幅接近电源轨。设计关键在于晶体管的尺寸(宽长比),需要根据所需的驱动电流、上升/下降时间以及功耗进行折衷优化。过大的驱动能力会增加开关噪声和功耗。

- 开漏输出:这种结构只有下拉NMOS管,没有内部上拉。输出高电平需要依赖外部上拉电阻连接到电源。开漏输出的主要优点是便于实现“线与”逻辑功能,以及方便进行不同电压域的电平转换(只需改变上拉电阻的电源电压)。在I2C等总线协议中广泛应用。但其缺点是上升时间由外部RC常数决定,速度较慢,且静态功耗可能较高。

- 三态输出:在总线应用中,多个驱动源需要共享同一物理线路。三态输出在推挽结构的基础上增加了一个使能控制端。当使能无效时,上下两个驱动管均关闭,输出呈现高阻态,从而与总线隔离。这使得多个器件可以分时复用总线而互不干扰。

三、双向输入/输出接口

许多芯片引脚(如存储器数据线、微控制器GPIO)需要根据操作模式在输入和输出功能间切换,这就需要双向I/O电路。其本质是输入缓冲器、输出驱动器和三态控制逻辑的巧妙组合,并通过方向控制信号进行管理。设计时需特别注意避免当方向切换瞬间或配置错误时,输出驱动与外部输入信号发生冲突(“争用”),导致大电流甚至损坏电路。

四、高速接口电路

随着数据速率进入Gb/s范围,接口设计面临信号完整性(如反射、串扰、码间干扰)的严峻挑战。此时,简单的CMOS推挽结构已力不从心。

- 电流模逻辑与低压差分信号:CML和LVDS采用差分信号传输,以恒定或受控的电流源驱动终端电阻。差分架构对共模噪声有极强的抑制能力,电压摆幅小(通常几百毫伏),开关速度快,功耗相对可控,是芯片间高速串行通信(如SerDes)的主流技术。

- 片上终端匹配:为了抑制高速信号在传输线末端的反射,需要在驱动器或接收器端集成匹配电阻(如50欧姆)。片上终端节省了PCB空间和元件,但需要精确的电阻工艺和校准电路来应对工艺、电压、温度的变化。

- 预加重与均衡:为了补偿信道的高频损耗,在发送端采用预加重技术,预先增强信号的高频分量;在接收端则采用均衡器(如连续时间线性均衡器CTLE或判决反馈均衡器DFE),来补偿衰减,睁开数据眼图。

接口电路的设计是CMOS集成电路设计中兼具艺术性与工程性的环节。设计师必须在驱动能力、速度、功耗、噪声、面积、可靠性以及系统兼容性之间做出精妙的权衡。随着工艺进步和系统需求日益复杂,接口电路,特别是高速SerDes和高速存储接口(如DDR/LPDDR),已成为许多SoC芯片中技术最密集、设计挑战最大的模块之一。理解并掌握各类接口电路的原理与设计方法,是成为一名优秀集成电路工程师的必经之路。

如若转载,请注明出处:http://www.mykmlife.com/product/55.html

更新时间:2026-04-18 00:11:10