零延时RS485接口集成电路设计与应用

在工业自动化、楼宇控制以及长距离数据通信等领域,RS485总线因其良好的抗干扰能力、支持多点通信和长距离传输等特性,成为广泛应用的标准。在高速或实时性要求极高的系统中,传统RS485接口电路存在的信号传输延时问题可能成为性能瓶颈。因此,设计一款“零延时”(或极低延时)的RS485接口集成电路具有重要的实际意义。

一、零延时RS485接口的设计挑战与目标

传统RS485接口的延时主要来源于几个方面:收发器内部逻辑处理延时、信号边沿转换速率(Slew Rate)限制、总线终端匹配以及电缆的传播延时。所谓“零延时”设计,并非完全消除物理定律决定的延时,而是通过优化集成电路架构和工艺,将收发器自身引入的延时降至最低,并优化系统设计以最小化整体链路延时。主要设计目标包括:

- 极低的收发转换延迟(Propagation Delay):从驱动端输入到总线输出,以及从总线接收到输出端的延迟需尽可能小。

- 高摆率与可控边沿:在满足EMI标准的前提下,采用更高的信号摆率,减少信号上升/下降时间,但同时需避免过冲和振铃。

- 快速的故障保护与恢复时间:在总线发生短路、开路等故障时,电路能快速进入保护状态并在故障消除后迅速恢复,减少系统死区时间。

- 低功耗与高可靠性:在追求速度的需兼顾功耗与ESD、浪涌防护等可靠性指标。

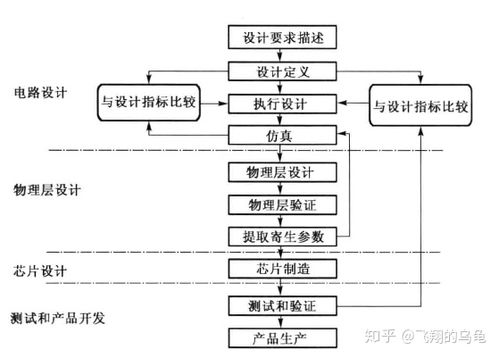

二、集成电路设计关键技术

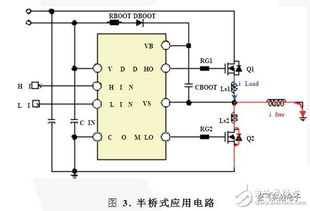

- 核心收发器架构优化:

- 采用高速、高精度的差分放大器作为接收器核心,通过优化偏置电路和增益级,减少信号检测与整形延时。

- 驱动级采用强驱动的CMOS或BiCMOS输出级,使用大尺寸晶体管并优化布局以降低输出阻抗,提升驱动能力和开关速度。

- 集成自适应边沿控制电路。通过检测总线负载情况,动态调整驱动电流,在轻负载时实现更快的边沿速率,在重负载或长电缆时自动降低边沿速率以抑制反射和EMI。

- 工艺选择与器件建模:

- 选用特征频率(fT)高的先进CMOS或BiCMOS工艺,以提升晶体管的开关速度。

- 对ESD保护结构进行精心设计,采用低电容的钳位电路(如TVS集成),避免保护二极管引入的寄生电容增加信号延时和边沿退化。

- 信号完整性设计:

- 在芯片内部,对关键高速信号路径(如差分输入/输出)进行对称布局和屏蔽,减少寄生效应和串扰。

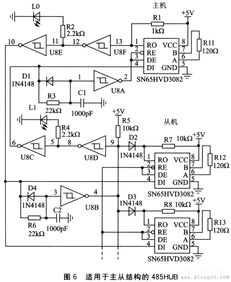

- 集成精密的片上终端电阻选项(如120Ω),其容差和温度系数需严格控制,以减少因外部元件不匹配引起的信号反射和延时抖动。

- 低延时控制逻辑:

- 使能(DE)和接收使能(RE)控制通路采用最短路径设计,其开关延时需与数据通道延时同步优化。

- 可考虑引入“自动方向控制”逻辑,通过监测本地发送数据活动自动切换收发状态,省去MCU控制延时,但这需要复杂的冲突检测与处理机制。

三、应用场景与系统设计考量

零延时RS485接口IC特别适用于以下场景:

- 高速工业运动控制网络:如伺服驱动器间的实时同步通信,微小的延时累积可能影响多轴协同精度。

- 电力系统继电保护与测控:要求数据在苛刻的噪声环境下被极速、可靠地传递。

- 高性能测量测试设备:多设备数据采集与触发信号的精确传输。

- 实时视频或大数据流的远距离传输(在RS485速率极限内)。

在系统应用时,为实现接近“零延时”的链路性能,需注意:

- 总线拓扑与终端匹配:尽量使用线性总线,并在两端精确匹配终端电阻。星型或分支过长的拓扑会引入反射,增加有效延时。

- 电缆选择:使用特性阻抗稳定(约120Ω)、衰减小的优质双绞线电缆。

- 电源与去耦:为RS485接口IC提供干净、低噪声的电源,并就近放置高质量的去耦电容,确保驱动瞬间的大电流需求。

- 接地与隔离:在噪声恶劣环境中,考虑使用隔离型的零延时RS485芯片或外接隔离模块,但需注意隔离器件自身会引入新的延时。

四、

零延时RS485接口集成电路的设计是一项在速度、可靠性、功耗和成本之间的综合权衡艺术。通过先进的芯片架构设计、工艺优化以及对信号完整性的深刻理解,可以显著降低RS485通信链路的固有延时,满足日益增长的工业实时通信需求。随着工艺进步和系统需求演进,集成更多智能功能(如延时补偿、在线诊断)的RS485接口芯片将成为工业互联网底层连接的关键部件。

如若转载,请注明出处:http://www.mykmlife.com/product/73.html

更新时间:2026-02-24 19:26:56